Transistor Ic Chip Ic Mpu I.Mx53 800mhz 529fbga de MCIMX537CVV8C

Datos del producto:

| Lugar de origen: | original |

| Nombre de la marca: | original |

| Certificación: | original |

| Número de modelo: | MCIMX537CVV8C |

Pago y Envío Términos:

| Cantidad de orden mínima: | 1 |

|---|---|

| Precio: | negotiation |

| Detalles de empaquetado: | Caja del cartón |

| Tiempo de entrega: | días 1-3working |

| Condiciones de pago: | T/T |

| Capacidad de la fuente: | 100.000 |

|

Información detallada |

|||

| Serie: | i.MX53 | paquete: | Bandeja |

|---|---|---|---|

| Situación del producto: | Obsoleto | Procesador de la base: | ARM® Cortex®-A8 |

| Número de corazones/de anchura del autobús: | 1 base, de 32 bits | Velocidad: | 800MHz |

| Co-Processors/DSP: | Multimedia; SIMD NEON™ | RAM Controllers: | LPDDR2, DDR2, DDR3 |

Descripción de producto

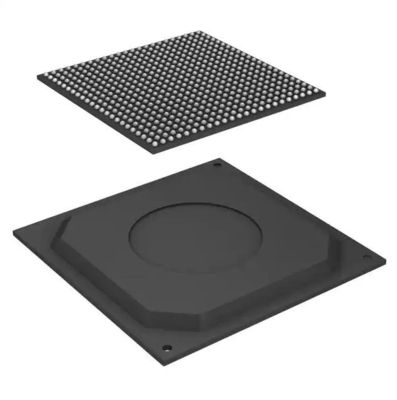

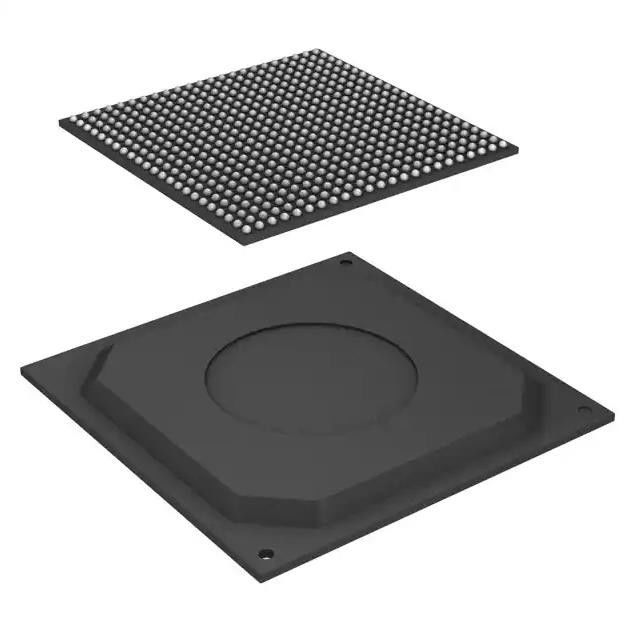

Transistor Ic Chip Ic Mpu I.Mx53 800mhz 529fbga de MCIMX537CVV8C

Base de IC i.MX53 1 del microprocesador de ARM® Cortex®-A8, 800MHz de 32 bits 529-FBGA (19x19)

Especificaciones de MCIMX537CVV8C

| TIPO | DESCRIPCIÓN |

| Categoría | Circuitos integrados (ICs) |

| Integrado | |

| Microprocesadores | |

| Mfr | NXP USA Inc. |

| Serie | i.MX53 |

| Paquete | Bandeja |

| Situación del producto | Obsoleto |

| Procesador de la base | ARM® Cortex®-A8 |

| Número de corazones/de anchura del autobús | 1 base, de 32 bits |

| Velocidad | 800MHz |

| Co-Processors/DSP | Multimedias; NEON™ SIMD |

| RAM Controllers | LPDDR2, DDR2, DDR3 |

| Aceleración de los gráficos | Sí |

| Reguladores de la exhibición y del interfaz | Telclado numérico, LCD |

| Ethernet | 10/100Mbps (1) |

| SATA | SATA 1.5Gbps (1) |

| USB | USB 2,0 (2), USB 2,0 + PHY (2) |

| Voltaje - entrada-salida | 1.3V, 1.8V, 2.775V, 3.3V |

| Temperatura de funcionamiento | -40°C ~ 85°C (TA) |

| Rasgos de seguridad | El BRAZO TZ, seguridad de la bota, criptografía, RTIC, Fusebox seguro, JTAG seguro, memoria segura, RTC seguro, trata de forzar la detección |

| Montaje del tipo | Soporte superficial |

| Paquete/caso | 529-FBGA |

| Paquete del dispositivo del proveedor | 529-FBGA (19x19) |

| Interfaces adicionales | 1-Wire, AC'97, PODER, ² C, ² S, MMC/SD, SAI, SPI, SSI, UART de I de I |

| Número bajo del producto | MCIMX537 |

Características de MCIMX537CVV8C

El procesador de usos de las multimedias i.MX53 (AP) se basa en la plataforma del BRAZO, que tiene características thefollowing:

• MMU, instrucción del L1 y escondrijo de los datos del L1

• Escondrijo unificado L2

• Frecuencia máxima de la base (escondrijo incluyendo de neón, de VFPv3 y del L1): 800 megaciclos

• Coprocesador de neón (medio de SIMD que procesa arquitectura) y coprocesador de la coma flotante del vector (VFP-Lite) que apoya VFPv3

• TrustZone el sistema de memoria consiste en los componentes siguientes:

• Llano 1 escondrijo:

— Instrucción (kilobyte 32)

— Datos (kilobyte 32)

• Escondrijo llano 2:

— Instrucción y datos unificados (kilobyte 256)

• Memoria (interna) del nivel 2:

— ROM de la bota, incluyendo HAB (kilobyte 64)

— Las multimedias internas/compartieron, RAM de rápido acceso (el kilobyte 128)

— RAM seguro/no-seguro (kilobyte 16)

• Interfaces externos de la memoria:

— 16/32-bit DDR2-800, LV-DDR2-800 o DDR3-800 hasta 2 Gbyte

— LPDDR2 de 32 bits

— flash de 8/16-bit NAND SLC/MLC, hasta 66 megaciclos, ECC 4/8/14/16-bit

— 8/16-bit NI flash, PSRAM, y RAM celular.

— modo multiplexado NI flash de 32 bits, PSRAM y RAM celular.

— (modo de DTACK) interfaz asincrónico de 8 bits de EIM.

— Todos los pernos de EIM muxed en otros interfaces (datos con los pernos de NFC). La lógica muxing de la entrada-salida selecciona el puerto de EIM, como muxing primario en la bota del sistema.

— Samsung OneNAND™ y manejó el NAND incluyendo eMMC hasta rev 4,4 (en I/Omode muxed)

El sistema i.MX53 se construye alrededor del sistema siguiente en interfaces del microprocesador:

• AMBA 64-bit AXI v1.0 autobús-utilizó por la plataforma del BRAZO, los aceleradores de las multimedias (tales como VPU, IPU, GPU3D, GPU2D) y el regulador externo de la memoria (EXTMC) que actuaba en 200 megaciclos.

• AMBA de 32 bits AHB 2,0 autobús-utilizó por el resto de los periférico del amo del autobús que actuaban en 133 megaciclos.

• autobús autobús-periférico de 32 bits del IP usado para el control (y el tráfico de datos lento) de la mayoría de los dispositivos periféricos del sistema que actúan en 66 megaciclos.

Usos de MCIMX537CVV8C

— Tres puertos I2S/SSI/AC97, apoyando hasta 1,4 Mbps, cada uno conectada con el audio

multiplexor

(AUDMUX) proporcionando cuatro puertos externos.

— Cinco puertos de UART RS232, hasta 4,0 Mbps cada uno. Uno apoya 8 el alambre, los otros cuatro

ayuda

4-wire.

— Dos puertos aumentados de alta velocidad de CSPI (ECSPI) más un puerto de CSPI

— Tres I2

Puertos de C, apoyando 400 Kbps

— Regulador rápido de Ethernet, diseñado para ser obediente con IEEE1588 V1, 10/100

Mbps

— Dos interfaces de la red del área del regulador (FlexCAN), 1 Mbps cada uno

— Sony Phillips Digital Interface (SPDIF), Rx y Tx

— Puerto dominante del cojín (KPP)

— Dos moduladores de la anchura de impulso (PWM)

— GPIO con capacidades de la interrupción

Clasificaciones ambientales y de la exportación de MCIMX537CVV8C

| CUALIDAD | DESCRIPCIÓN |

| Situación de RoHS | ROHS3 obediente |

| Nivel de la sensibilidad de humedad (MSL) | 3 (168 horas) |

| Situación del ALCANCE | ALCANCE inafectado |

| ECCN | 5A992C |

| HTSUS | 8542.31.0001 |

![]()

Quiere saber más detalles sobre este producto